XJTAG - XJDeveloper Full test development environment software

- Reduce your time spent debugging boards due to high precision fault isolation

- Improve your time to market and reduce project risk by early design verification

- Reduce your test development time by reusing tests from prototype/design in manufacturing and field support

- Ongoing time savings by test reuse across projects

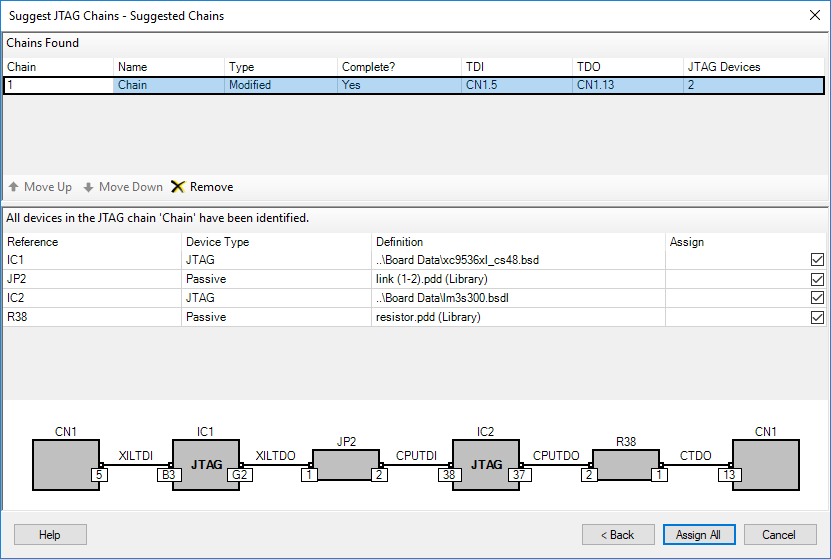

XJDeveloper is an Integrated Development Environment for JTAG test development and execution. Through its intuitive design flow, engineers have easy access to XJTAG’s market-leading interconnection and functionality-based testing technology. This is supported by a large built-in library of device tests, combined with the ability to easily develop additional tests. Advanced fault analysis and visualisation tools are included as standard. XJDeveloper also supports In-System Programming (including XJFlash) of both JTAG devices (e.g. CPLDs and FPGAs) and non-JTAG devices (EEPROMs, flash memory).

XJDeveloper gives engineers easy access to the functionality defined in IEEE 1149 (JTAG). This standard can be used throughout the entire product lifecycle to bring the benefits of boundary scan testing to any product, however complex. Projects are focussed on the devices being tested. XJTAG’s powerful processing technology automatically creates the low-level test vectors without the user needing to know how to construct them. Test coverage can be viewed at any point in the project setup to assess setup progress or see how the design can be improved. When the project is complete, XJDeveloper can create XJRunner projects for testing and programming on the production line.

XJDeveloper can be used to run tests during prototype bring-up without the need for any application code to be ready. Using the same user interface that will later be used for production line testing ensures a smooth test flow from prototype debug to production test.

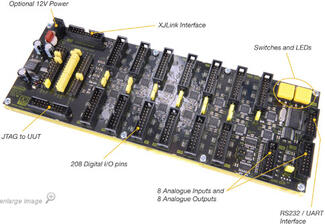

XJDeveloper supports all of the test capabilities of XJTAG’s full product line-up, to give you full flexibility for all of your JTAG testing requirements.

Testing Connections

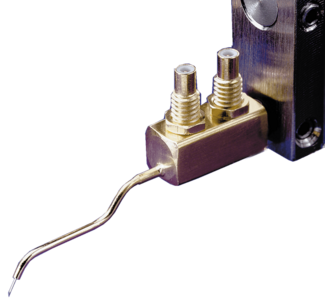

Boundary scan testing using XJDeveloper starts with XJTAG’s Advanced Interconnection Test. This is able to test a higher percentage of a circuit than most other JTAG solutions, and is automatically generated from the data given during test setup. The interconnection test provides the core of the test coverage for your board, checking JTAG-accessible nets for short-circuit, stuck-high/stuck-low faults, and open-circuit errors. The test includes checks for missing pull-up/pull-down resistors and resistive short-circuit errors. It also dynamically drives the logic devices in the circuit, giving test coverage to the nets which are accessible to JTAG only through logic devices.

XJEase Model Library

After the interconnection test, XJTAG continues by running tests written in the XJEase language, that are normally from XJTAG’s built-in test library. The tests use the functionality of the devices on the board to verify that they are present and connected correctly. Because XJEase is a fully-featured programming language, these tests are dynamic, and are written to react to the conditions they find on the board.

Device-Centric Tests

XJTAG’s library tests are device-centric – they are specific to the type of device being tested but not to the circuit they are placed in, or to the JTAG devices that are used to drive the nets on the PCB. This means that tests can simply be added to the project and re-used without modification whenever that type of device is re-used in other projects. Over time, this greatly reduces the engineering costs of project setup with XJTAG.

As a user, you can access the source code for each test provided in XJTAG’s library, and the full-range of XJEase debugging facilities in XJDeveloper. It is therefore possible to verify the operation of the tests, modify them, or adapt them for new or future device types.

Fault Analysis

The main purpose of a JTAG test system is to detect faults in PCB assemblies, but the true value of this system is in its ability to accurately identify the cause of the faults.

XJDeveloper can find and identify a wide range of faults. Information about the faults can be combined with imported Netlist and Schematic diagrams to graphically show the nets exhibiting faults. Nets can be highlighted on both the Schematic Diagram and the PCB layout, using XJDeveloper’s viewer tools. The Schematic Viewer and Layout Viewer are also accessible in XJRunner, XJTAG’s production test environment, and XJInvestigator, the advanced fault diagnosis/rework station.

These powerful features, provided as standard, take fault analysis to a new level. Being able to see all of the points on a net where a short-circuit may have occurred due to a manufacturing defect, for example, can save valuable time in rework.

In-System Programming

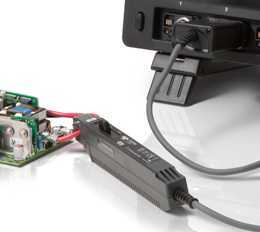

In-System Programming (ISP) through a JTAG tool provides a simple way of configuring non-volatile memory during or after PCB assembly. XJDeveloper can be used to perform In-System Programming of flash and FPGA/CPLDs.

JTAG can be used to configure programmable devices of any size, by serially shifting address, data and control information through the JTAG chain to the relevant device. This is perfect for smaller devices such as EEPROMs that contain a serial number, for example. However, using this method for in-system programming larger images, such as an entire file system, would lead to programming times that are too long for a production environment. The answer to this is hardware-accelerated programming.

Accelerated Programming

XJTAG has used its expertise in JTAG to offer industry-leading solutions to engineers who are faced with the challenge of delivering faster hardware-accelerated programming over a boundary scan interface. This may involve the temporary reconfiguration of an FPGA on a board as an ‘in-system programmer’. This advanced technique allows XJTAG to program large non-volatile flash memories, with the speed often being limited by the device being programmed. XJTAG calls this solution XJFlash. It has been shown to result in programming cycle times that are 50 times faster than just using boundary scan test. In some cases, the programming times are even faster than a manufacturer’s published figures.

XJDeveloper offers a range of acceleration options, including XJFlash for programming using FPGAs or CPLDs, and XJDirect, which programs using an on-board CPU or Microcontroller. Other applications may have more unusual requirements, and for such boards, XJTAG offers a consultancy service to develop bespoke solutions. Any programmable devices on a board can be used to deliver the desired results at high speed. Please contact us if you would like to know more.

Features

- Advanced Interconnection Test - Tests a higher percentage of your circuit than most other JTAG solutions and provides high precision fault isolation.

- Testing and programming non-JTAG devices - Non-JTAG devices connected to devices on the chain can be manipulated just as easily as those on the chain, for advanced testing – e.g. ethernet loopback.

- Flexible, high-level, test description language - Designed to simplify the process of test creation.

- Device-centric approach - Device tests can be reused in different circuits without modification.

- High-level conditional test execution - Determine whether to run tests based on board configuration, results of previous tests etc.

- Built-in Test Library - A large number of standard parts available in the installed XJEase library.

- Layout Viewer to show the physical location of circuit elements and faulty nets.

- Schematic Viewer to show circuit functionality whilst developing or debugging tests.

- Open test implementations - Users can view the data driven during connection test, and view or edit code from the XJEase library.

- Waveform View - View a graphical representation of waveforms in XJEase testing and in the Analyser screen.

- XJEase software debugger - Step through XJEase code, set breakpoints and examine variable values to speed up your test development.

- No need to understand how JTAG works - The XJTAG system works out how to drive the JTAG chains for you.

- Program devices in-system - SVF and STAPL files can be run from XJDeveloper to program devices, or XJEase scripts can be used to program an image directly.

- Testing with no netlist - Run connection test and non-JTAG device tests even on boards where you don’t have the netlist.

- Export projects to XJRunner - XJRunner projects prevent modification of the tests for deployment to manufacture.

- Test coverage analysis - Analyse and generate reports on the test coverage achieved on your circuit.

- 1149.6 support - Supports 1149.1 and 1149.6 devices