Products

Displaying 25 - 35 of 35

Simplifies test setup with inline operation and automated discovery

Tests across a wide range of protocols

Modifies real-world network traffic and CRCs

Triggers protocol analyzers or other test instruments at the error injection point

The APEX Turbine Data System (DS) is the next generation of data acquisition, control, setup, and online analysis. It reliably acquires time-synchronized data from a network of digitizers, regardless of sample rate or sensor type.

Intuitive, icon-based setup and control

Spreadsheet-style channel configuration

Snapshot display with data export

Autonomous Modal Parameter Estimation Procedure

Multiple Live Parameter Estimation Windows

Task Oriented, Easy-To-Use Interface

Only BSDL files required to get the board up and running

Set up pin states – e.g. low, high, toggling

Trace shorts, opens and other signals

Easy low-level access to device pins/busses

Clear display of the pins/balls with variable zoom levels and split screen

View JTAG chain data as waveforms

Quickly find and monitor changing pins

Program devices with SVF and STAPL files

Real-time interaction

XJIntegration (use XJAnalyser functionality from other software)

Reduce your time spent debugging boards due to high precision fault isolation

Improve your time to market and reduce project risk by early design verification

Reduce your test development time by reusing tests from prototype/design in manufacturing and field support

Ongoing time savings by test reuse across projects

Reduce flash programming times

SPI, QSPI, parallel NOR flash devices supported

Support for NAND flash devices available on request

Shortened development cycles

No need for additional equipment

Can be used for fast firmware upgrade

No FPGA development required

Repair-focused environment for XJDeveloper / XJRunner tests.

Full Connection test.

RAM, Flash and other non-JTAG device tests.

Flash, FPGA, CPLD and EEPROM programming.

Layout Viewer* to show the physical location of faulty nets, pins and components.

Schematic Viewer* to show the circuit design around faults.

Direct control of the pins/balls of JTAG devices.

View pin states graphically in real time or capture them in the Waveform Viewer.

Trace signals to identify shorts, opens and other faults.

Improves your QA through configurable logging

Allows you to retain power of control on how boards are tested by third parties

User-friendly environment reduces your training costs for production operatives

Ability to test multiple boards, simultaneously, by using multiple XJLinks

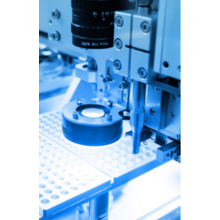

Solve machine vision applications efficiently by constructing flowcharts instead of writing program code, using field-proven tools for analyzing, classifying, locating, measuring, reading and verifying

Use a single program for creating both application logic and operator interface

Leverage deep learning for visual inspection through image classification and segmentation tools

Rely on a common underlying vision library for the same results with an Iris GTX smart camera, vision systems or third-part computer

Work with multiple cameras all within the same project or per project running concurrently and independently from one another, platform permitting

Solve applications rather than develop underlying tools by leveraging a toolkit with a more than 25-year history of reliable performance

Tackle applications with utmost confidence using field-proven tools for analyzing, classifying, locating, measuring, reading and verifying

Base analysis on monochrome and color 2D images as well as 3D profiles, depth maps and point clouds

Harness the full power of today's hardware through optimizations exploiting SIMD, multi-core CPU and multi-CPU technologies

Support platforms ranging from smart cameras to HPCs via a single consistent and intuitive API